高端路由器设计需要考虑的数据缓冲器问题

迅速增加的数据、语音和视频流量进入城域网(MAN)后,服务于这些应用的路由器必须能将多路的1 Gbps数据流汇聚成高达40 Gbps带宽的数据流.为了保持线速性能,系统必须在出口端提供等于或高于进入传输速率的信息包处理能力,或者对信息包进行备份,这时缓冲就变得至关重要。

这些数据缓存的性能和效率对路由器和网络的性能至关重要。网络性能的主要威胁来自数据的重发。因此,城域边缘的路由器必须能够汇聚多个较低速率的接入线路,并将其转发至高速核心连接而不致欠载。路由器也必须保证从更高速的核心网到边缘网的数据分发操作不会超时。在任何情况下超过了数据缓存的最大能力,发送到 MAN 的任何额外数据都必须重传。

因此,最大限度地降低系统延迟和确保系统最大吞吐量的关键是为具体应用选择合适的数据缓存。如果缓存过大,就会大幅度增加系统成本。如果过小,网络就会溢出缓存并重发数据,导致性能下降。

这种考虑涉及三个主要因素:输入数据的速率(入口线路)、输出数据的速率(出口线路)及内部处理时间需求。只要来自网络的入口数据速率与回到网络的出口数据速率相等,而且具有最小的处理需求,数据缓存即可保持相对较小。因为内部处理只增加很小的延迟,流量也比较稳定,所以几乎不需要存储数据。不过,随着系统执行更高级别的处理,就必须增大缓存来消除处理功能带来的延迟。突发流量对数据缓存的设计也有显著的影响。如果入口数据速率随着时间显著变化并偶尔超过信息包处理器的能力,就必须适当地改变入口缓冲器的尺寸,以解决与这些处理功能相关的延迟问题。

可编程逻辑器件的优势

在为这些应用构建缓冲子系统时,工程师倾向于首先考虑采用FPGA,而不是现成的分立存储器件。由于工程教育机构日益依赖于 FPGA 来教授电路设计的基础知识。因此,大部分工程师都熟悉这种技术。FPGA 有助于设计师随时对他们的设计进行重新配置,提供高度灵活性,并在短期内完成硬件的测试。此外,由于这些工具常常是人们熟悉的,可以迅速转变成最终解决方案。

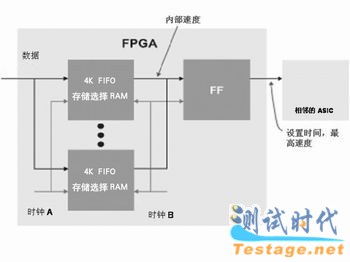

现在,FPGA 可提供数百万的逻辑门和兆比特级的片上存储器,设计师可将多个 FIFO集成到一个芯片上(见图 1)。然而,在数据缓存需求比较高的城域边缘网领域,设计师必须仔细评估他们所有的设计选择。在某些情况下,设计师会发现可编程逻辑器件在给定性能或成本方面存在固有的局限性,而分立器件可提供更具吸引力的解决方案。

图1 可集成多个FIFO的FPGA